18.11.2013 21:44

Триггер, как класс электронных устройств.

Триггер (триггерная система) — класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов. Каждое состояние триггера легко распознаётся по значению выходного напряжения. По характеру действия триггеры относятся к импульсным устройствам — их активные элементы (транзисторы) работают в ключевом режиме, а смена состояний длится очень короткое время.

Отличительной особенностью триггера как функционального устройства является свойство запоминания двоичной информации. Под памятью триггера подразумевают способность оставаться в одном из двух состояний и после прекращения действия переключающего сигнала. Приняв одно из состояний за «1», а другое за «0», можно считать, что триггер хранит (помнит) один разряд числа, записанного в двоичном коде.

При изготовлении триггеров применяются преимущественно полупроводниковые приборы (обычно биполярные и полевые транзисторы).

Используются, в основном, в вычислительной технике для организации компонентов вычислительных систем: регистров, счётчиков, процессоров, ОЗУ.

Триггеры подразделяются на две большие группы — динамические и статические. Названы они так по способу представления выходной информации.

Динамический триггер представляет собой систему, одно из состояний которой (единичное) характеризуется наличием на выходе непрерывной последовательности импульсов определённой частоты, а другое — отсутствием выходных импульсов (нулевое). Смена состояний производится внешними импульсами (рис. 3). Динамические триггеры в настоящее время используются редко.

Рис. 3

К статическим триггерам относят устройства, каждое состояние которых характеризуется неизменными уровнями выходного напряжения (выходными потенциалами): высоким — близким к напряжению питания и низким — около нуля. Статические триггеры по способу представления выходной информации часто называют потенциальными.

Статические (потенциальные) триггеры, в свою очередь, подразделяются на две неравные по практическому значению группы — симметричные и несимметричные триггеры. Оба класса реализуются на двухкаскадном усилителе с положительной обратной связью, а названием своим они обязаны способам организации внутренних электрических связей между элементами схемы.

Симметричные триггеры отличает симметрия схемы и по структуре, и по параметрам элементов обоих плеч. Для несимметричных триггеров характерна неидентичность параметров элементов отдельных каскадов, а также и связей между ними.

Симметричные статические триггеры составляют основную массу триггеров, используемых в современной радиоэлектронной аппаратуре. Схемы симметричных триггеров в простейшей реализации (2х2ИЛИНЕ) показаны на рис. 4.

Рис.4 Схемы симметричных триггеров в простейшей реализации (2х2ИЛИНЕ).

Основной и наиболее общий классификационный признак — функциональный — позволяет систематизировать статические симметричные триггеры по способу организации логических связей между входами и выходами триггера в определённые дискретные моменты времени до и после появления входных сигналов. По этой классификации триггеры характеризуются числом логических входов и их функциональным назначением.

Вторая классификационная схема, независимая от функциональной, характеризует триггеры по способу ввода информации и оценивает их по времени обновления выходной информации относительно момента смены информации на входах.

Каждая из систем классификации характеризует триггеры по разным показателям и поэтому дополняет одна другую. К примеру, триггеры RS-типа могут быть в синхронном и асинхронном исполнении.

Асинхронный триггер изменяет своё состояние непосредственно в момент появления соответствующего информационного сигнала(ов), с некоторой задержкой равной сумме задержек на элементах составляющих данный триггер.

Синхронные триггеры реагируют на информационные сигналы только при наличии соответствующего сигнала на так называемом входе синхронизации С (от англ. clock). Этот вход также обозначают термином «такт». Такие информационные сигналы называют синхронными. Синхронные триггеры в свою очередь подразделяют на триггеры со статическим (статические) и динамическим (динамические) управлением по входу синхронизации С.

Одноступенчатые триггеры состоят из одной ступени представляющей собой элемент памяти и схему управления, делятся на триггеры со статическим управлением и триггеры с динамическим управлением.

Триггеры со статическим управлением воспринимают информационные сигналы при подаче на вход С логической единицы (прямой вход) или логического нуля (инверсный вход).

Триггеры с динамическим управлением воспринимают информационные сигналы при изменении (перепаде) сигнала на входе С от 0 к 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход). Также встречается название «триггер управляемый фронтом».

Двухступенчатые триггеры бывают, как правило, со статическим управлением. При одном уровне сигнала на входе С информация, в соответствии с логикой работы триггера, записывается в первую ступень (вторая ступень заблокирована для записи). При другом уровне этого сигнала происходит копирование состояния первой ступени во вторую (первая ступень заблокирована для записи), выходной сигнал появляется в этот момент времени с задержкой равной задержке срабатывания ступени. Обычно двухступенчатые триггеры применяются в схемах, где логические функции входов триггера зависят от его выходов, во избежание временны́х гонок. Двухступенчатые триггеры с динамическим управлением встречаются крайне редко. Двухступенчатый триггер обозначают ТТ.

Описание работы триггера.

Триггер — это запоминающий элемент с двумя (или более) устойчивыми состояниями, изменение которых происходит под действием входных сигналов и предназначен для хранения одного бита информации, то есть лог. 0 или лог. 1.

Все разновидности триггеров представляют собой элементарный автомат, включающий собственно элемент памяти (ЭП) и комбинационную схему (КС), которая может называться схемой управления или входной логикой (рис. 5).

Рис. 5 Структура триггеров в виде КС и ЭП

В графе триггера каждая вершина графа соединена со всеми другими вершинами, при этом переходы от вершины к вершине возможны в обе стороны (двухсторонние). Граф двоичного триггера — две точки соединённые отрезком прямой линии, троичного триггера — треугольник, четверичного триггера — квадрат с диагоналями, пятеричного триггера — пятиугольник с пентаграммой и т. д. При N=1 граф триггера вырождается в одну точку, в математике ему соответствует унарная единица или унарный ноль, а в электронике — монтажная «1» или монтажный «0», то есть простейшее ПЗУ. Устойчивые состояния имеют на графе триггера дополнительную петлю, которая обозначает, что при снятии управляющих сигналов триггер остаётся в установленном состоянии.

Состояние триггера определяется сигналами на прямом и инверсном выходах. При положительном кодировании (позитивная логика) высокий уровень напряжения на прямом выходе отображает значение лог. 1 (состояние = 1), а низкий уровень — значение лог. 0 (состояние = 0). При отрицательном кодировании (негативная логика) высокому уровню (напряжению) соответствует логическое значение «0», а низкому уровню (напряжению) соответствует логическое значение «1».

Изменение состояния триггера (его переключение или запись) обеспечивается внешними сигналами и сигналами обратной связи, поступающими с выходов триггера на входы схемы управления (комбинационной схемы или входной логики). Обычно внешние сигналы, как и входы триггера, обозначают латинскими буквами R, S, T, C, D, V и др. В простейших схемах триггеров отдельная схема управления (КС) может отсутствовать. Поскольку функциональные свойства триггеров определяются их входной логикой, то названия основных входов переносятся на всю схему триггера.

Входы триггеров разделяются на информационные (R, S, T и др.) и управляющие (С, V). Информационные входы предназначены для приема сигналов запоминаемой информации. Названия входных сигналов отождествляют с названиями входов триггера. Управляющие входы служат для управления записью информации. В триггерах может быть два вида управляющих сигналов:

синхронизирующий (тактовый) сигнал С, поступающий на С-вход (тактовый вход);

разрешающий сигнал V, поступающий на V-вход.

На V-входы триггера поступают сигналы, которые разрешают (V=1) или запрещают (V=0) запись информации. В синхронных триггерах с V-входом запись информации возможна при совпадении сигналов на информационном С и V-входах.

Работа триггеров описывается с помощью таблицы переключений, являющейся аналогом таблицы истинности для комбинационной логики. Выходное состояние триггера обычно обозначают буквой Q. Индекс возле буквы означает состояние до подачи сигнала (t) либо (t-1) или после подачи сигнала (t+1) или (t). В триггерах с парафазным (двухфазным) выходом имеется второй (инверсный) выход, который обозначают как Q, /Q или Q'.

RS-триггер асинхронный

| S |

R |

Q(t) |

Q(t) |

Q(t+1) |

Q(t+1) |

| 0 |

0 |

0 |

1 |

0 |

1 |

| 0 |

0 |

1 |

0 |

1 |

0 |

| 0 |

1 |

0 |

1 |

0 |

1 |

| 0 |

1 |

1 |

0 |

0 |

1 |

| 1 |

0 |

0 |

1 |

1 |

0 |

| 1 |

0 |

1 |

0 |

1 |

0 |

| 1 |

1 |

0 |

1 |

не определено |

не определено |

| 1 |

1 |

1 |

0 |

не определено |

не определено |

Асинхронный RS-триггер с инверсными входами

RS-триггер — триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё выходное состояние при подаче на один из его входов единицы.

При подаче единицы на вход S (от англ. Set — установить) выходное состояние становится равным логической единице. А при подаче единицы на вход R(от англ. Reset — сбросить) выходное состояние становится равным логическому нулю. Состояние, при котором на оба входа R и S одновременно поданы логические единицы, в простейших реализациях является запрещённым (так как вводит схему в режим генерации), в более сложных реализациях RS-триггер переходит в третье состояние QQ=00. Одновременное снятие двух «1» практически невозможно. При снятии одной из «1» RS-триггер переходит в состояние, определяемое оставшейся «1». Таким образом RS-триггер имеет три состояния, из которых два устойчивых (при снятии сигналов управления RS-триггер остаётся в установленном состоянии) и одно неустойчивое (при снятии сигналов управления RS-триггер не остаётся в установленном состоянии, а переходит в одно из двух устойчивых состояний).

RS-триггер используется для создания сигнала с положительным и отрицательным фронтами, отдельно управляемыми посредством стробов, разнесённых во времени.

RS-триггеры иногда называют RS-фиксаторами.

RS-триггер синхронный

| C |

S |

R |

Q(t) |

Q(t+1) |

| 0 |

x |

x |

0 |

0 |

| 1 |

1 |

| 1 |

0 |

0 |

0 |

0 |

| 1 |

0 |

0 |

1 |

1 |

| 1 |

0 |

1 |

0 |

0 |

| 1 |

0 |

1 |

1 |

0 |

| 1 |

1 |

0 |

0 |

1 |

| 1 |

1 |

0 |

1 |

1 |

| 1 |

1 |

1 |

0 |

не определено |

| 1 |

1 |

1 |

1 |

не определено |

Схема синхронного RS-триггера совпадает со схемой одноступенчатого парафазного (двухфазного) D-триггера, но не наоборот, так как в парафазном (двухфазном) D-триггере не используются комбинации S=0, R=0 и S=1, R=1.

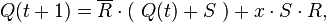

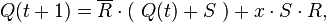

Алгоритм функционирования синхронного RS-триггера можно представить формулой

-

где x — неопределённое состояние.

D-триггер синхронный

Пример D-триггера с динамическим синхронным входом С и с дополнительными асинхронными инверсными входами S и R

| D |

Q(t) |

Q(t+1) |

| 0 |

0 |

0 |

| 0 |

1 |

0 |

| 1 |

0 |

1 |

| 1 |

1 |

1 |

D-триггер (D от англ. delay — задержка) — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. После прихода активного фронта импульса синхронизации на вход С D-триггер открывается. Сохранение информации в D-триггерах происходит после спада импульса синхронизации С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, парафазный (двухфазный) D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно игверсные сигналы.

D-триггер (D от англ. delay — задержка) — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. После прихода активного фронта импульса синхронизации на вход С D-триггер открывается. Сохранение информации в D-триггерах происходит после спада импульса синхронизации С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, парафазный (двухфазный) D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно игверсные сигналы.

D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине.

В одноступенчатых D-триггерах во время прозрачности все изменения информации на входе D передаются на выход Q. Там, где это нежелательно, нужно применять двухступенчатые (двухтактные, Master-Slave, MS) D-триггеры.

T-триггер асинхронный

Асинхронный Т-триггер не имеет входа разрешения переключения Т, поэтому переключение триггера в противоположное состояние происходит при изменении логического уровня на входе С.

T-триггер синхронный

| T |

Q(t) |

Q(t+1) |

| 0 |

0 |

0 |

| 0 |

1 |

1 |

| 1 |

0 |

1 |

| 1 |

1 |

0 |

Условное графическое обозначение (УГО) синхронного T-триггера с динамическим входом синхронизации С на схемах.

Синхронный Т-триггер, при единице на входе Т, по каждому такту на входе С изменяет своё логическое состояние на противоположное, и не изменяет выходное состояние при нуле на входе T. Т-триггер может строиться на JK-триггере, на двухступенчатом (Master-Slave, MS) D-триггере и на двух одноступенчатых D-триггерах и инверторе. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединяя входы J и К. Наличие в двухступенчатом (Master-Slave, MS) D-триггере динамического входа С позволяет получить на его основе T-триггер. При этом инверсный выход Q соединяется со входом D, а на вход С подаются счётные импульсы. В результате триггер при каждом счётном импульсе запоминает значение  , то есть будет переключаться в противоположное состояние.

, то есть будет переключаться в противоположное состояние.

Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена на 2.

Счётчик числа импульсов.

Счётчик числа импульсов — устройство, на выходах которого получается двоичный (двоично-десятичный) код, определяемый числом поступивших импульсов. Счётчики могут строиться на T-триггерах. Основной параметр счётчика — модуль счёта — максимальное число единичных сигналов, которое может быть сосчитано счётчиком. Счётчики обозначают через СТ (от англ. counter).

Счётчики классифицируют:

по числу устойчивых состояний триггеров

-на двоичных триггерах

-на троичных триггерах

-на n-ичных триггерах

по модулю счёта:

-двоично-десятичные (декада);

-двоичные;

-с произвольным постоянным модулем счёта;

-с переменным модулем счёта;

по направлению счёта:

-суммирующие;

-вычитающие;

-реверсивные;

по способу формирования внутренних связей:

-с последовательным переносом;

-с параллельным переносом;

-с комбинированным переносом;

-кольцевые;

по способу переключения триггера:

-синхронные;

-асинхронные;

Дешифратор.

Дешифраторы - это комбинационные схемы с несколькими входами и выходами, преобразующие код, подаваемый на входы в сигнал на одном из выходов. На выходе дешифратора появляется логическая единица, на остальных — логические нули, когда на входных шинах устанавливается двоичный код определённого числа или символа, то есть дешифратор расшифровывает число в двоичном, троичном или k-ичном коде, представляя его логической единицей на определённом выходе. Число входов дешифратора равно количеству разрядов поступающих двоичных, троичных или k-ичных чисел. Число выходов равно полному количеству различных двоичных, троичных или k-ичных чисел этой разрядности.

Для n-разрядов на входе, на выходе 2n, 3n или kn. Чтобы вычислить, является ли поступившее на вход двоичное, троичное или k-ичное число известным ожидаемым, инвертируются пути в определённых разрядах этого числа. Затем выполняется конъюнкция всех разрядов преобразованного таким образом числа. Если результатом конъюнкции является логическая единица, значит на вход поступило известное ожидаемое число.

Из логических элементов являющихся дешифраторами можно строить дешифраторы на большое число входов. Каскадное подключение таких схем позволит наращивать число дифференцируемых переменных.

Структурная схема дешифратора (а) и обозначение дешифратора на принципиальных электрических схемах (б) приведена ниже:

D-триггер (D от англ. delay — задержка) — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. После прихода активного фронта импульса синхронизации на вход С D-триггер открывается. Сохранение информации в D-триггерах происходит после спада импульса синхронизации С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, парафазный (двухфазный) D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно игверсные сигналы.

D-триггер (D от англ. delay — задержка) — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. После прихода активного фронта импульса синхронизации на вход С D-триггер открывается. Сохранение информации в D-триггерах происходит после спада импульса синхронизации С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, парафазный (двухфазный) D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно игверсные сигналы. , то есть будет переключаться в противоположное состояние.

, то есть будет переключаться в противоположное состояние.

УЧЕНЬЕ - СВЕТ, А НЕУЧЕНЬЕ - ЧУТЬ СВЕТ И НА РАБОТУ!

УЧЕНЬЕ - СВЕТ, А НЕУЧЕНЬЕ - ЧУТЬ СВЕТ И НА РАБОТУ!